|

如今的 7nm EUV 芯片,晶体管多达 100 亿个,它们是怎么样安上去的呢?

9 {8 n k! }4 e晶体管并非是安装上去的,芯片制造其实分为沙子 - 晶圆,晶圆 - 芯片这样的过程,而在芯片制造之前,IC 设计要负责设计好芯片,然后交给晶圆代工厂。

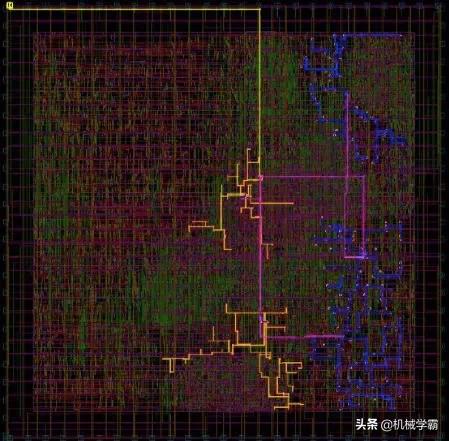

$ o, Q f8 m2 O6 Q |$ [芯片设计分为前端设计和后端设计,前端设计(也称逻辑设计)和后端设计(也称物理设计)并没有统一严格的界限,涉及到与工艺有关的设计就是后端设计。芯片设计要用专业的 EDA 工具。

5 W0 C- W! _# L# ~

: t; {' e8 _$ H+ p; _6 w& @8 D3 f- e

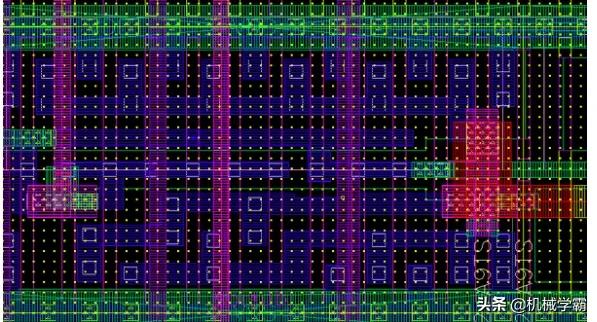

- L4 l4 O' g h+ f! p如果我们将设计的门电路放大,白色的点就是衬底,还有一些绿色的边框就是掺杂层。 * K% P& s+ ]4 G6 B6 K5 k9 w3 w

$ }$ ]2 S' a3 A $ }$ ]2 S' a3 A

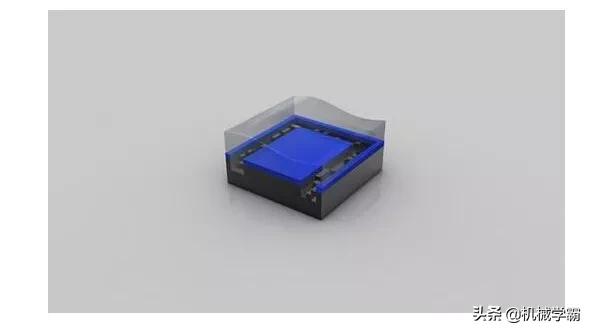

4 @- k3 ?4 X5 f! K$ N- \: G6 J当芯片设计好了之后,就要制造出来,晶体管就是在晶圆上直接雕出来的,晶圆越大,芯片制程越小,就能切割出更多的芯片,效率就会更高。

! j6 K0 G& D9 G, I; h举个例子,就好像切西瓜一样,西瓜更大的,但是原来是切成 3 厘米的小块,现在换成了 2 厘米,是不是块数就更多。所以现在的晶圆从 2 寸、4 寸、6 寸、8 寸到现在 16 寸大小。

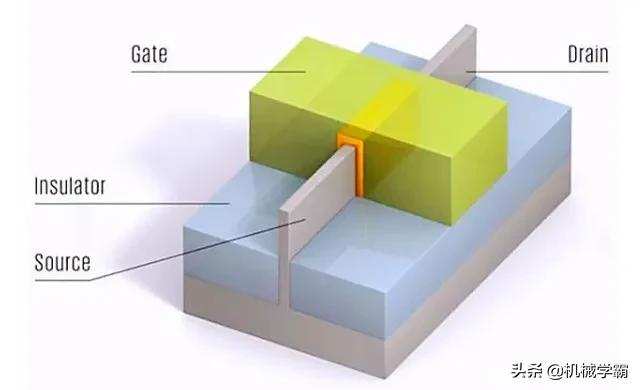

" k d- o: K1 n: L制程这个概念,其实就是栅极的大小,也可以成为栅长,它的距离越短,就可以放下更多的晶体管,这样就不会让芯片不会因技术提升而变得更大,使用更先进的制造工艺,芯片的面积和功耗就越小。但是我们如果将栅极变更小,源极和漏极之间流过的电流就会越快,工艺难度会更大。

2 B J, d! v5 t- G+ M8 r/ m

) O; ]( t( X( E8 O% S- N ) O; ]( t( X( E8 O% S- N

0 J' {% ?9 ?. p z- \- p$ d

芯片制造共分为七大生产区域,分别是扩散、光刻、刻蚀、离子注入、薄膜生长、抛光、金属化。

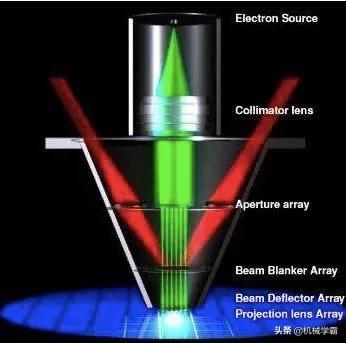

; k& Z4 G% \ v T其中雕出晶圆的最重要的两个步骤就是光刻和蚀刻,光刻技术是一种精密的微细加工技术。

: N/ o+ }1 ]( L" c2 u5 r7 {

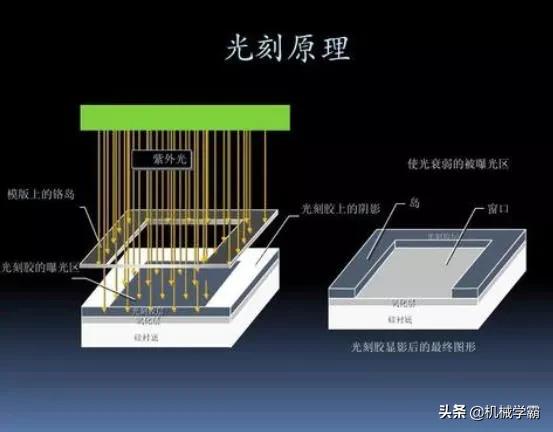

常规光刻技术是采用波长为 2000~4500 的紫外光作为图像信息载体,以光致抗光刻技术蚀剂为中间(图像记录)媒介实现图形的变换、转移和处理,最终把图像信息传递到晶片(主要指硅片)或介质层上的一种工艺。

! u2 \* p* ?7 e! p: g9 k- Y

g3 [6 l& V! ~4 O u; C. K g3 [6 l& V! ~4 O u; C. K

) i) C3 e, |2 E- ]7 G8 x& c光刻技术就是把芯片制作所需要的线路与功能区做出来。简单来说芯片设计人员设计的线路与功能区“印进”晶圆之中,类似照相机照相。 " N" R$ w# b5 g4 P' f$ b' }# b: n

照相机拍摄的照片是印在底片上,而光刻刻的不是照片,而是电路图和其他电子元件。 # W; S' ` |$ u4 ?& s' n7 z8 ?

) A( N+ ^ ~+ F9 B9 O# O/ b) G ) A( N+ ^ ~+ F9 B9 O# O/ b) G

, |1 U( ?# S* u# L: u

而蚀刻技术就是利用化学或物理方法,将抗蚀剂薄层未掩蔽的晶片表面或介质层除去,从而在晶片表面或介质层上获得与抗蚀剂薄层图形完全一致的图形。 6 F7 y' e# ]: U

集成电路各功能层是立体重叠的,因而光刻工艺总是多次反复进行。例如,大规模集成电路要经过约 10 次光刻才能完成各层图形的全部传递。 * {' q0 C6 |, l

在半导体制造中有两种基本的刻蚀工艺:干法刻蚀和湿法腐蚀。目前主流所用的还是干法刻蚀工艺,利用干法刻蚀工艺的就叫等离子体蚀刻机。 - U4 T! ?& y% D

在集成电路制造过程中需要多种类型的干法刻蚀工艺,应用涉及硅片上各种材料。被刻蚀材料主要包括介质、硅和金属等,通过与光刻、沉积等工艺多次配合可以形成完整的底层电路、栅极、绝缘层以及金属通路等。

; u& B: o2 ^4 B8 |( a4 U$ a9 R1 H: ~

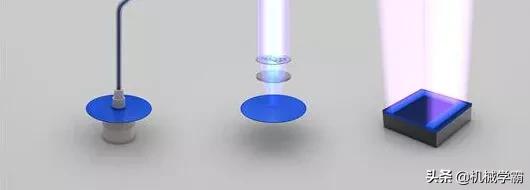

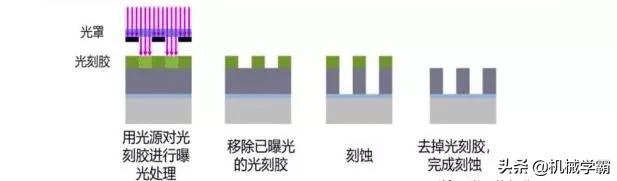

% S$ G5 H+ x. c在涂满光刻胶的晶圆(或者叫硅片)上盖上事先做好的光刻板,然后用紫外线隔着光刻板对晶圆进行一定时间的照射。原理就是利用紫外线使部分光刻胶变质,易于腐蚀。

, J+ A( T2 r0 r! n8 e

+ o9 Y/ D" ^1 M# g' I- l3 D( Y8 F/ K4 v3 Y

溶解光刻胶:光刻过程中曝光在紫外线下的光刻胶被溶解掉,清除后留下的图案和掩模上的一致。  0 [0 H: ?5 c& b6 f' f8 D1 t: ? 0 [0 H: ?5 c& b6 f' f8 D1 t: ?

( z. W7 N0 W# p/ a, u“刻蚀”是光刻后,用腐蚀液将变质的那部分光刻胶腐蚀掉(正胶),晶圆表面就显出半导体器件及其连接的图形。然后用另一种腐蚀液对晶圆腐蚀,形成半导体器件及其电路。

) w' f$ m6 c- g* f3 G3 {# M" w% Q

清除光刻胶:蚀刻完成后,光刻胶的使命宣告完成,全部清除后就可以看到设计好的电路图案。

" Z% v. y3 a3 _' q$ Y! y0 O8 V

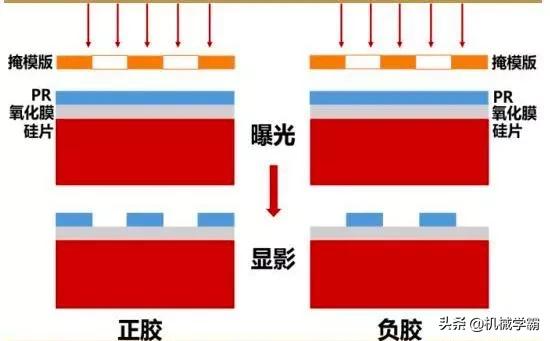

! O# T- M$ q* b5 m$ Z这里说一下,什么是光刻胶。我们要知道电路设计图首先通过激光写在光掩模版上,然后光源通过掩模版照射到附有光刻胶的硅片表面,引起曝光区域的光刻胶发生化学效应,再通过显影技术溶解去除曝光区域或未曝光区域,使掩模版上的电路图转移到光刻胶上,最后利用刻蚀技术将图形转移到硅片上。  8 E* i @7 l3 t6 M8 k" s 8 E* i @7 l3 t6 M8 k" s

" i* L( c% k' f: T$ B

而光刻根据所采用正胶与负胶之分,划分为正性光刻和负性光刻两种基本工艺。在正性光刻中,正胶的曝光部分结构被破坏,被溶剂洗掉,使得光刻胶上的图形与掩模版上图形相同。 ; i* W7 }# n0 @4 v/ Y- @9 K

相反地,在负性光刻中,负胶的曝光部分会因硬化变得不可溶解,掩模部分则会被溶剂洗掉,使得光刻胶上的图形与掩模版上图形相反。  6 Q' U. t: n& N" z' { 6 Q' U. t: n& N" z' {

! ^* E1 H) i+ W" q1 K可以说,在晶圆制造中,直径 30 厘米的圆形硅晶薄片穿梭在各种极端精密的加工设备之间,由它们在硅片表面制作出只有发丝直径千分之一的沟槽或电路。 6 K4 u$ y4 k4 G

热处理、光刻、刻蚀、清洗、沉积……每块晶圆要昼夜无休地被连续加工两个月,经过成百上千道工序,最终集成了海量的微小电子器件,经切割、封装,成为信息社会的基石——芯片。 s5 T; |) e' N2 E! j' F3 P" E

! u) F0 m' k m+ h( S ! u) F0 m' k m+ h( S

1 ?& t% v8 m( R, \4 n) v

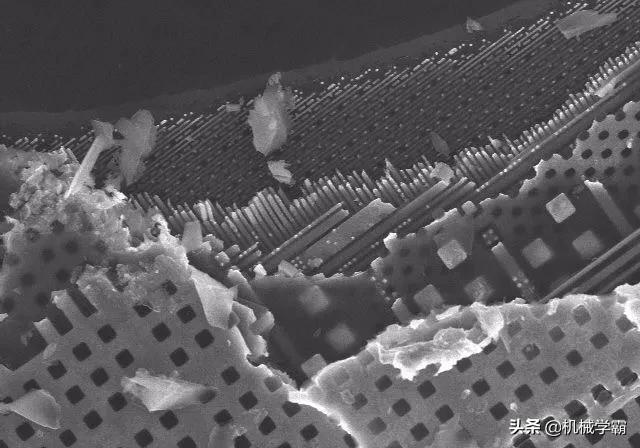

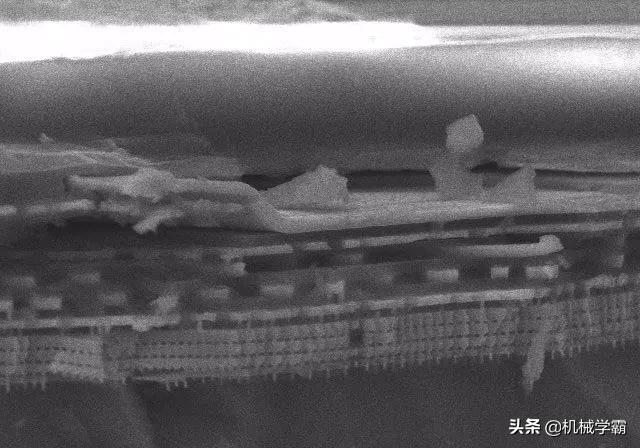

这是一个 Top-down View 的 SEM 照片,可以非常清晰的看见 CPU 内部的层状结构,越往下线宽越窄,越靠近器件层。 ' N) x/ F6 A3 `

4 z- e3 L% q( ~) \5 H0 j: @' l8 P3 v* w# S8 }8 i

这是 CPU 的截面视图,可以清晰地看到层状的 CPU 结构,由上到下有大约 10 层,其中最下层为器件层,即是 MOSFET 晶体管。 H2 \: j7 N4 C5 p, a$ |

. U/ @+ F- [5 Z$ |/ r& v* S- Q- ~9 v* N

*来源:胖福的小木屋 原文地址 https://baijiahao.baidu.com/s?id=1661518867399354763&wfr=spider&for=pc |